Quad-Apollo MxFE : beamforming bande X 16Tx/16Rx (concept de référence)

Quad-Apollo MxFE : un sous-système de beamforming numérique à échantillonnage direct en bande X à 16 émetteurs / 16 récepteurs Concept de référence

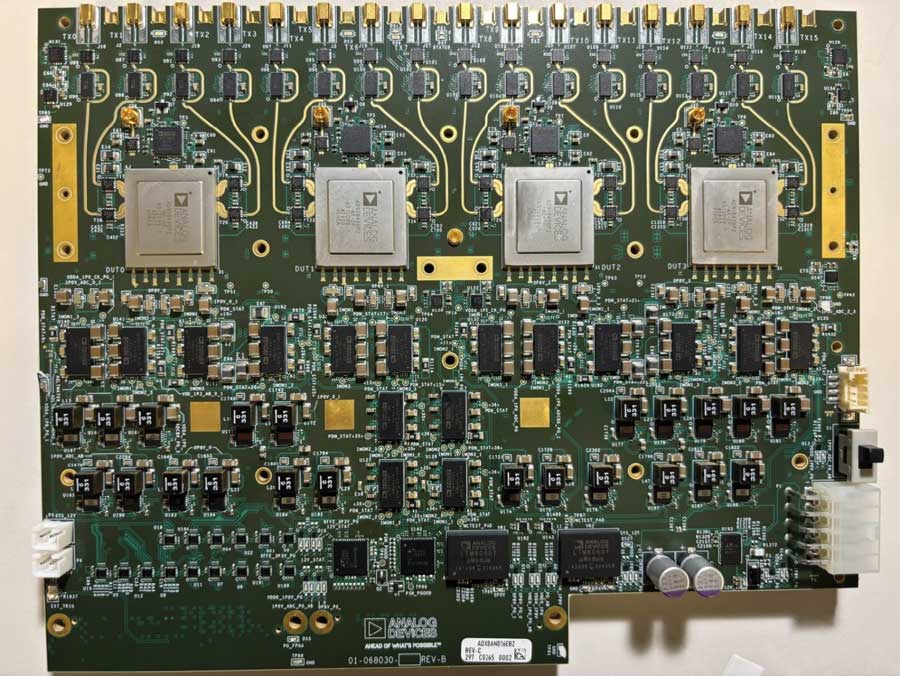

Cet article présente la conception et la mise en œuvre de la plateforme de beamforming numérique en bande X Quad-Apollo MxFE™ (module frontal à signal mixte), une architecture de référence avancée pour l’échantillonnage direct-RF, développée pour démontrer toutes les capacités de la technologie Apollo MxFE d’Analog Devices. La plateforme intègre quatre transceivers 4Tx/4Rx avec horloge synchronisée, déclenchement déterministe et synchronisation à cohérence de phases, afin de permettre un véritable beamforming numérique sur 16 canaux d’émetteur et 16 canaux de récepteur, sur les fréquences de la bande X. Une chaîne de signal complète ainsi qu’une synchronisation multipuce sont mises en œuvre pour réaliser un réseau à cohérence de phase évolutif capable d’effectuer des opérations large bande et de prendre en charge le multibeam.

La plateforme de beamforming numérique à échantillonnage direct en bande X Quad-Apollo MxFE™ (module frontal à signal mixte) est une architecture de référence complète pour les systèmes de beamforming numérique de nouvelle génération. Conçue pour mettre en lumière les capacités de la technologie MxFE® d’Analog Devices, elle intègre tous les sous-systèmes essentiels (conditionnement du signal RF, horloge de précision, synchronisation multipuce et gestion des alimentations) dans un environnement intégré à haute performance qui prend en charge le traitement de signal cohérent et évolutif sur de multiples canaux.

Chaque sous-réseau à l’intérieur de la plateforme comprend 16 canaux d’émetteur et 16 canaux de récepteur configurés en un réseau linéaire uniforme, avec un espacement des éléments correspondant à une demi longueur d’onde à 12 GHz. Cette géométrie permet un échantillonnage spatial optimal pour le fonctionnement dans la bande X, en prenant en charge le beamforming entièrement numérique à travers tous les éléments. La plateforme montre qu’il est possible de parfaitement synchroniser et cadencer ensemble plusieurs convertisseurs de données AD9084 Apollo MxFE dans une architecture cohérente. Elle offre ainsi un exemple réaliste d’intégration au niveau du système pour les applications RF multicanal.

La plateforme Quad-Apollo MxFE est à la fois un concept de référence1 et un outil d’évaluation et de développement polyvalent pour les systèmes de radar et de communication avancés. Son architecture prend en charge plusieurs faisceaux simultanés, l’annulation adaptative et les modèles de faisceaux reconfigurables, ce qui permet d’obtenir la flexibilité nécessaire aux applications modernes de radars à réseau phasé, de guerre électronique et de détection multimission. La structure de synchronisation déterministe du système, le module frontal haut débit et le schéma de synchronisation évolutive forment ensemble une chaîne de signal complète (de l’entrée RF à la sortie en faisceau numérique) destinée à accélérer l’innovation dans le domaine des technologies de réseau numérique haut débit.

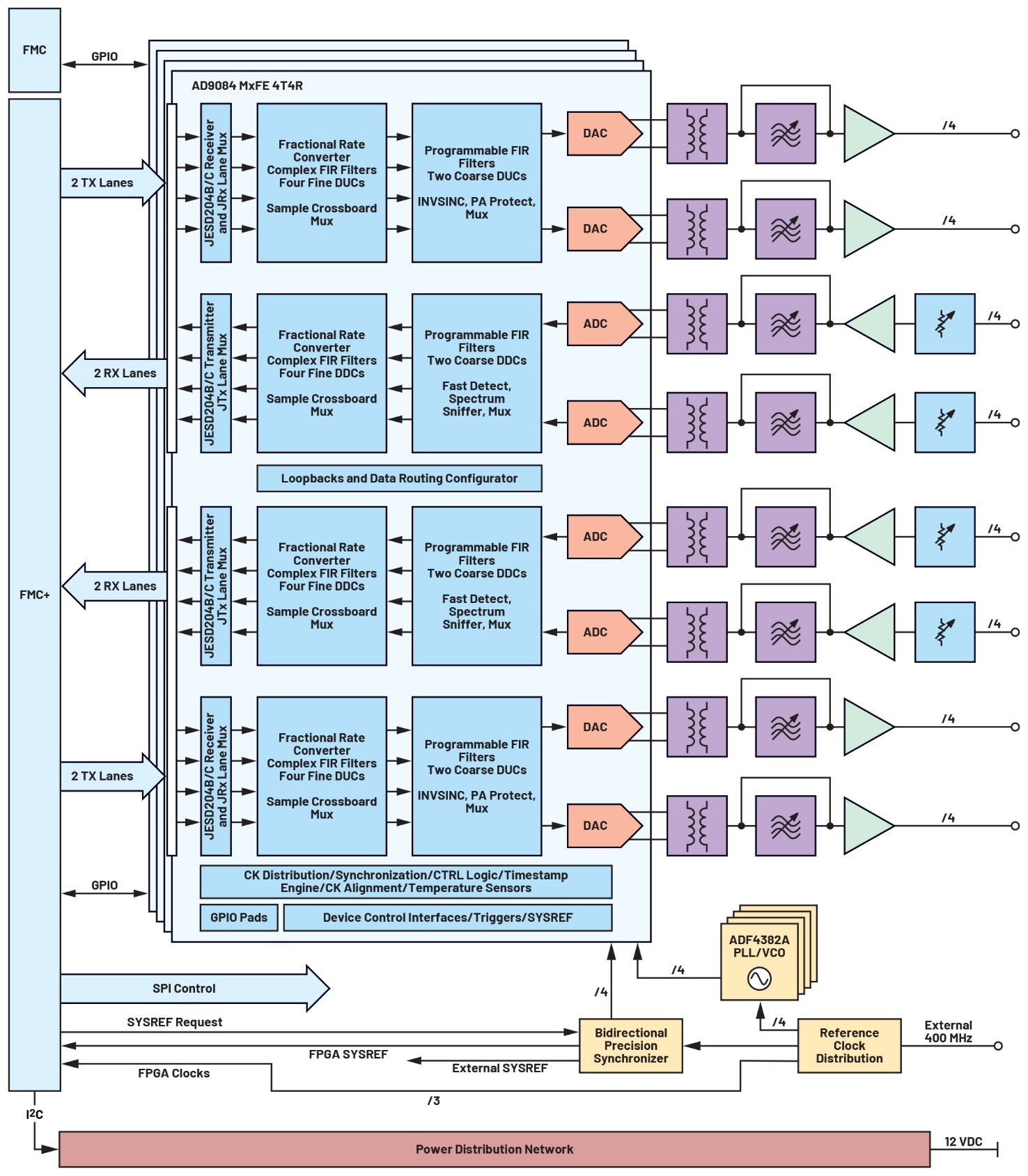

Le schéma fonctionnel de la figure 2 illustre la chaîne de signal du module frontal RF émetteur-récepteur d’un unique sous-réseau, le convertisseur de données doté de fonctions de traitement de signal numérique durci, la solution d’horloge multipuce et la solution de puissance 12 V DC. L’utilisation d’une carte porteuse FPGA avec des pilotes logiciels open-source de bas niveau et des boîtes à outils MATLAB® permet de contrôler la plateforme du système par logiciel2,3.

Module frontal RF

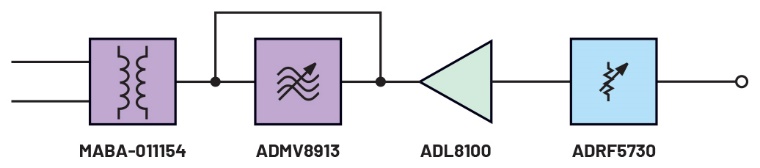

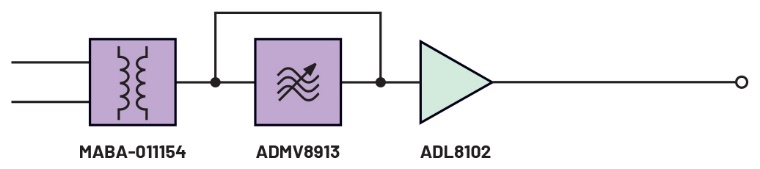

Le module frontal RF du système Quad-Apollo MxFE est conçu avec simplicité et modularité mettant l’accent sur la flexibilité, la performance et la facilité de personnalisation pour des applications diverses. Comme illustré dans les figures 3 et 4, l’architecture utilise des chemins de signaux haut débit et peu complexes pour couvrir de nombreuses fréquences, tout en maintenant une haute linéarité et l’intégrité du signal d’un bout à l’autre de la chaîne.

Au cœur de cette architecture, le concept utilise des baluns haut débit 2:1 pour assurer l’interface entre les ADC et DAC à haute vitesse et le reste de la chaîne de signal analogique. Chaque canal de transceiver intègre un filtre bande X ajustable numériquement et partagé (ADMV8913), ce qui assure une sélection de fréquence précise et le rejet hors bande. Cette phase de filtrage inclut un chemin de contournement au niveau de la carte qui peut être déclenché par un mécanisme de rotation du condensateur, permettant ainsi un échantillonnage direct dans les fréquences des bandes S, C et Ku. Lorsque le filtre est contourné, le système sacrifie les avantages d’anti-repliement de l’ADMV8913 au profit d’une plus grande flexibilité de fréquence pour les applications haut débit ou large bande où le filtrage peut être traité numériquement.

Du côté du récepteur, chaque canal est doté d’un amplificateur à faible bruit (LNA) haut débit modeste mais hautement linéaire, suivi d’un atténuateur à paliers numérique (DSA) large bande au niveau de l’entrée. Le DSA permet un contrôle de gain analogique précis avec des conditions de signal variables, et il est directement contrôlé via l’interface GPIO (general-purpose input output) du convertisseur de données, pour un réglage déterministe rapide quand le système est en fonctionnement. Cette architecture supporte les reconfigurations rapides, ce qui en fait une solution particulièrement efficace pour les systèmes de beamforming adaptatifs ou en temps réel.

Les concepteurs ont particulièrement veillé à la linéarité du récepteur, car les produits de distorsion d’intermodulation ont tendance à être spatialement corrélés à travers les éléments d’un système de réseau phasé entièrement numérique. La technologie Quad-Apollo MxFE garantit par conséquent le maintien de la plage dynamique et de la pureté spectrale, y compris dans des configurations cohérentes multicanal.

Pour les applications exigeant une translation de fréquences supplémentaire, des étages de gain ou un conditionnement spécial du signal, la plateforme prend en charge l’intégration de cartes enfichables spécifiques en amont du module frontal. Il est donc possible de définir une enveloppe de performance répondant aux exigences spécifiques de l’utilisation finale, qu’il s’agisse d’optimiser la bande passante, le facteur de bruit ou la couverture de fréquences. En conservant une chaîne de signal simple et haut débit au niveau du sous-réseau, le système Quad-Apollo MxFE offre un socle à la fois flexible et robuste pour le développement de systèmes RF à haute performance et évolutifs.

Architecture d’horloge

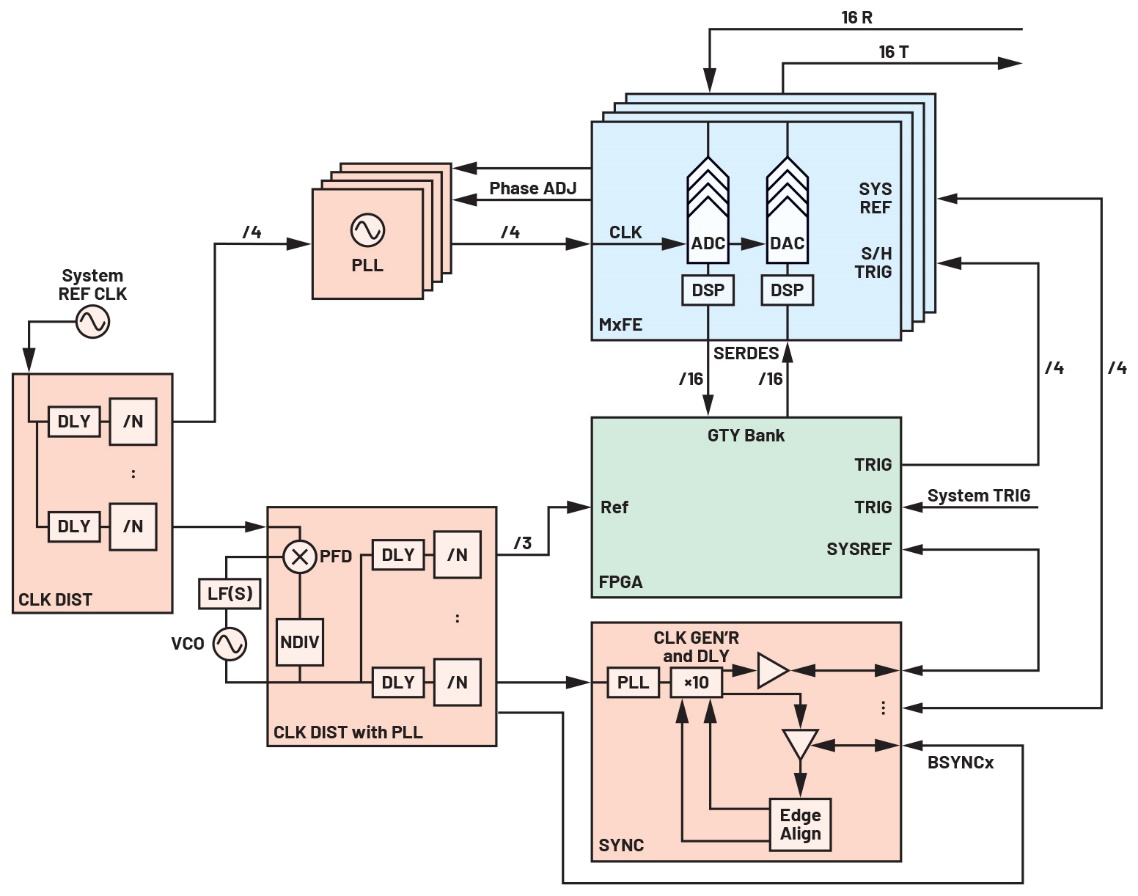

L’horloge joue un rôle essentiel dans les systèmes multiconvertisseurs, car elle permet la synchronisation multipuce, la latence déterministe et la cohérence des signaux à travers de vastes architectures distribuées. Une distribution d’horloge précise garantit que chaque convertisseur de données, FPGA et module frontal analogique fonctionne de manière parfaitement synchronisée — une exigence majeure pour les radars à réseau phasé, les instrumentations à canaux multiples ou les systèmes de communication avancés, par exemple.

Dans ces systèmes, la synchronisation JESD204C est obtenue en combinant des blocs de génération et de distribution d’horloges dédiés, complétés par un synchroniseur bidirectionnel de sous-classe 1. Cette architecture garantit la latence déterministe sur tous les canaux JESD204C, et les concepteurs peuvent ainsi prévoir et contrôler la synchronisation à la nanoseconde près. Le schéma de synchronisation peut en outre être étendu à plusieurs sous-systèmes, en maintenant la latence déterministe à travers plusieurs sous-réseaux pour les mises en œuvre de grande échelle.

Comme illustré sur la figure 5, une unique horloge de référence à haute stabilité sert de base pour l’ensemble du réseau de synchronisation. Cette référence est distribuée à travers des tampons fanout d’horloges à très faible gigue qui alimentent les dispositifs MxFE avec des horloges d’échantillonnage présentant des bruits de phase ultrabas et exceptionnellement propres. Chaque dispositif MxFE emploie une interface d’horloge différentielle qui maintient en continu l’alignement de la phase et de la fréquence, en compensant les dérives dues aux variations de température ou aux effets du vieillissement à long terme.

La même référence (master) pilote un étage secondaire de génération d’horloge visant à produire des horloges numériques pour le FPGA et fournir des signaux de référence de précision au synchroniseur. Le mécanisme de coordination est conçu autour d’un synchroniseur de précision à 10 canaux envoyant des signaux de synchronisation à basse fréquence bidirectionnels qui alignent tous les convertisseurs de données et le FPGA sur une référence de synchronisation commune. Ce synchroniseur permet également de régler les retards de propagation par canal, et donc d’ajuster précisément l’alignement et les relations de phases entre les canaux, afin d’optimiser la performance.

Selon l’architecture globale du réseau, le synchroniseur peut être déployé dans des configurations daisy-chain ou fanout, ce qui garantit une synchronisation évolutive à travers des sous-réseaux ou partitions système multiples. Même en fonctionnant avec des vitesses d’échantillonnage extrêmement élevées (jusqu’à 20 GSPS), l’infrastructure d’horloge maintient l’alignement déterministe, en assurant la cohérence des phases et l’intégrité de la synchronisation dans l’ensemble du système. En associant une horloge à faible gigue, une distribution hiérarchique et une synchronisation de sous-classe 1 JESD204C, toute la plateforme dispose d’une structure de synchronisation unifiée à phase stable qui soutient l’acquisition de données à haute vitesse et la performance du traitement des signaux.

Tableau 1. Applications du Quad-Apollo MxFE

|

Horloge de référence système (MHz) |

Horloge d’échantillonnage (GSPS) |

Vitesse d’échantillonnage CAN (GSPS) |

Vitesse d’échantillonnage CNA (GSPS) |

JESD204C Vitesse de voie (GBPS) |

Vitesse de décimation |

Vitesse de voie (MSPS) |

Bande passante instantanée utilisable (MHz) |

|

400 |

12,8 |

12,8 |

25,6 |

13,2 |

32 |

400 |

320 |

|

400 |

12,8 |

12,8 |

25,6 |

26,4 |

16 |

800 |

640 |

|

400 |

20 |

20 |

20 |

20,625 |

16 |

625 |

500 |

Le tableau 1 présente trois configurations d’exploitation représentatives du système Quad-Apollo MxFE avec une horloge de référence de 400 MHz. Ensemble, ces trois configurations illustrent les compromis entre la vitesse d’échantillonnage, la décimation numérique et le débit des données lors de l’optimisation de la bande passante et de la performance de l’interface pour différentes exigences système.

Conclusion

La validation système de la plateforme de beamforming numérique en bande X Quad-Apollo MxFE™ confirme un fonctionnement cohérent sur tous les canaux, en obtenant un alignement des phases de niveau inférieur et une précision de la synchronisation inférieure à la picoseconde. La performance démontrée dans l’orientation de faisceau adaptative, l’annulation spatiale et la transmission multibeam indique que la plateforme est prête à émuler des architectures de radars et de guerre électronique de nouvelle génération.

Ces résultats marquent une étape importante dans la réalisation de systèmes de beamforming numérique évolutifs. D’autres articles étudieront prochainement plus en détail les dimensions techniques de la plateforme Quad-Apollo MxFE, en s’appuyant sur cette base pour révéler tout le potentiel des architectures d’échantillonnage direct-RF et mettre en œuvre les futurs réseaux définis par logiciel à haute performance.

Références

1 ADXBAND16EBZ Prototyping Platform User Guide. Analog Devices Wiki.

2 AMD Virtex™ UltraScale+™ FPGA VCU118 Evaluation Kit. AMD.

3 https://github.com/analogdevicesinc/HighSpeedConverterToolbox

À propos de l’auteur

Siddhartha Das est ingénieur d’applications systèmes au sein de l’équipe Subsystems and Sensors de l’unité opérationnelle Aerospace, Defense, and Communications d’Analog Devices, à Durham, en Caroline du Nord. Il a obtenu un diplôme en génie électrique (Bachelor of Science) à la Virginia Tech en 2023, où il prépare actuellement un Master of Science dans la même discipline.

Chez ADI, Siddhartha travaille sur le développement, l’intégration et la caractérisation de sous-systèmes de réseaux phasés avancés. Sa mission couvre les chaînes de signaux RF à haute performance, les plateformes de beamforming numérique et les techniques de synchronisation multipuce, et il contribue également à des travaux concernant les systèmes radars et de communication de nouvelle génération.

Source : com-trail.com